Proceedings of the 16th Conference on Formal Methods in Computer-Aided Design (FMCAD 2016) Mountain View, California, USA, October 3 - 6, 2016

Edited by Ruzica Piskac and Muralidhar Talupur

In cooperation with ACM Special Interest Group on Programming Languages ACM Special Interest Group on Software Engineering

SIG OFT

🐵 SIGPLAN

Technical co-sponsorship of IEEE Council on Electronic Design Automation

Proceedings of the 16th Conference on

## Formal Methods in Computer-Aided Design

### **FMCAD 2016**

October 3 - 6, 2016

Mountain View, California, USA

Edited by Ruzica Piskac and Muralidhar Talupur

ISBN: 978-0-9835678-6-8 Copyright owned jointly by the authors and FMCAD Inc. Title page: Photo provided with limited rights.

### Preface

The International Conference on Formal Methods in Computer-Aided Design (FMCAD) is a series of meetings presenting groundbreaking results on the theory and application of rigorous formal techniques for the automated design of systems. The FMCAD conference covers the entire spectrum of formal aspects of specification, verification, synthesis, and testing, and is a leading forum for researchers and practitioners in academia and industry alike. The sixteenth meeting in the series was held in Mountain View, California, USA, October 3-6, 2016.

FMCAD 2016 featured a high quality program comprised of five parts: a memorial session for Professor Helmut Veith, one of the original co-chairs for this event, a tutorial day with four tutorials, a series of invited talks by experts in areas adjoining formal methods, a student forum, and finally the main program consisting of the accepted papers.

Before his unexpected passing, Helmut Veith was one of the key persons in shaping this event. We have endeavored to stay true to his vision by creating a program that is informative, high quality, and enjoyable at the same time. We had a memorial session for Helmut with talks by his collaborators and friends. This was a followed by a keynote by Professor Christos Papadimitriou on algorithms and evolution. Helmut was excited about having this talk at FMCAD and we were glad that Professor Papadimitriou was able to give this talk.

This year FMCAD featured exciting keynote talks not just from formal methods, but also from adjoining areas:

- Formal Verification for Computer Security: Lessons Learned and Future Directions by Dawn Song (UC Berkeley)

- Understanding Evolution through Algorithms by Christos Papadimitriou (UC Berkeley)

- Network Verification When Clarke Meets Cerf by George Varghese (UCLA)

All these talks were given by well known experts, possibly outside the traditional topics at FMCAD, but were crucial for expanding horizons of the formal methods community. The talk on evolution, in particular, was not connected to formal methods, but we honored Helmut's wish to have a fun invited talk on the latest advances in the broader field of Computer Science.

The tutorial day featured four tutorials, given below in the order of presentation. These gave the audience both a look into the latest developments in the field, and a retrospective on formal methods in the industry.

- Machine Learning and Systems for the Next Frontier in Formal Verification by Manish Pandey, Synopsys Inc.

- Verifying Hyperproperties of Hardware Systems by Bernd Finkbeiner (Saarland University) and Markus Rabe (UC Berkeley)

- A Paradigm Shift in Verification Methodology by Pranav Ashar (RealIntent)

- Program Synthesis for Networks by Pavol Černý (University of Colorado Boulder)

FMCAD also offered the fourth edition of the Student Forum, organized by Hossein Hojjat (Rochester Institute of Technology). The Forum is described in more detail later in these proceedings.

For the main program, we received 64 submissions, resulting in 23 high quality accepted papers. Each paper was reviewed by at least four reviewers. The authors were then given the opportunity to respond to the comments and correct any misunderstanding. This rebuttal phase lasted a week and was followed by discussions among the reviewers to converge on a final score for the paper.

The final set of accepted papers ranged from protocol verification, architectural specification capture, traditional hardware, software verification, SMT solvers, program synthesis, and verification of timed systems. During the conference each paper was presented by one of the authors followed by a brief Q&A. Each regular paper was allotted 30 minutes and the three short papers were allotted 15 minutes each.

A conference with such a diverse program and audience as FMCAD relies on a large number of people supporting the organization. The program committee members are too numerous to list individually; we thank each and every one of them for their time, dedication to the purpose of FMCAD, their willingness to help the authors improve their manuscripts, and their help with additional tasks such as selecting and reviewing papers for the Best Paper Award. Our sincere gratitude further goes out to the Publication Chair Florian Zuleger (Vienna University of Technology, Austria; in charge of these proceedings). Hossein Hojjat (Rochester Institute of Technology) took over the non-trivial task of serving as Student Forum Chair; his engagement and enthusiasm for the process ensured an encouragingly large number of Student Forum submissions. Special thanks goes to Jens Katelaan (Vienna University of Technology, Austria) and Keshav Kini (University of Texas at Austin) formally the Webchairs, creating and maintaining a snappy new FMCAD website. The conference would not be possible without the tireless efforts of our Local Chairs Sean Safarpour (Synopsys) and Divjyot Sethi (Cisco) who made all the arrangements for conference to take place. Sean in particular worked with Synopsys management to host FMCAD at its facilities and ultimately save us quite a bit of expenses. As always, the FMCAD Steering Committee was available with both guidance and encouragement whenever needed, and even when not. We thank Armin Biere (Johannes Kepler University in Linz, Austria), Alan Hu (University of British Columbia, Canada), Warren A. Hunt, Jr. (University of Texas at Austin), and Vigyan Singhal (Oski Technology).

We would like to express our gratitude to our industrial sponsors Amazon, Cadence Design Systems, Cisco Systems, FMCAD, Inc., IBM, Infosys, Mentor Graphics, OneSpin Solutions, Oski Technology, and Synopsys. for their continued financial support of the FMCAD community. The National Science Foundation and FMCAD Inc. provided generous funds in support of the Student Forum, without which this event would simply not be possible.

FMCAD 2016 once again received in-cooperation status with ACM under the Special Interest Groups on Programming Languages (SIGPLAN) and on Software Engineering (SIGSOFT). It also received technical sponsorship from the IEEE Council on Electronic Design Automation. The FMCAD 2016 Proceedings are available through the ACM Digital Library, the IEEE Xplore Digital Library, and are also available as a free download from the FMCAD Website.

At the heart of the conference are, of course, the accepted papers, the tutorials, and the keynotes; we thank all presenters for their efforts to devote a significant portion of their time to FMCAD. We are grateful to all authors of submissions, accepted or not, and all attendees of FMCAD 2016, for playing their part in making FMCAD a continued success story.

Finally, we would like to dedicate these proceedings to Helmut Veith, our cherished friend, and colleague. He will be dearly missed both as a collaborator and a friend.

Ruzica Piskac and Muralidhar Talupur FMCAD 2016 Program Chairs Mountain View, California, October 2016.

### **Organization Committee**

Program Co-Chairs Ruzica Piskac Muralidhar Talupur

Yale University FormalSim

### Local Arrangement Chairs & Webmasters Sean Safarpour Synopsys Divjyot Sethi Cisco Jens Katelaan Technical Keshav Kini University

Synopsys Cisco Technical University of Vienna University of Texas Austin

Publication Chair Florian Zuleger

Technical University of Vienna

### Student Forum Chair

Hossein Hojjat

Rochester Institute of Technology

### **Steering Committee**

Armin Biere Alan J. Hu Warren A. Hunt, Jr. Vigyan Singhal

Johannes Kepler University in Linz, Austria University of British Columbia, Canada University of Texas at Austin, USA Oski Tech

### Program Committee

Pranav Ashar Domagoj Babic Armin Biere Roderick Bloem Ahmed Bouajjani Gianpiero Cabodi Supratik Chakraborty Leonardo de Moura Michael Emmi Malay Ganai Arie Gurfinkel Ziyad Hanna Fei He Keijo Heljanko Warren Hunt Himanshu Jain Gerwin Klein Daniel Kroening Shuvendu Lahiri Rebekah Leslie-Hurd Panagiotis Manolios Kenneth McMillan John O'Leary Lee Pike Ruzica Piskac Ahmed Rezine Sean Safarpour Divjyot Sethi Natasha Sharygina Sharon Shoham Muralidhar Talupur Michael Tautschnig Helmut Veith Tomas Vojnar Chao Wang Eran Yahav Florian Zuleger

Real Intent Google Johannes Kepler University Graz University of Technology LIAFA, University Paris Diderot Politecnico di Torino **IIT Bombay** Microsoft Research IMDEA Software Institute **Synopsys** University of Waterloo Cadence Design System School of Software, Tsinghua University Aalto University University of Texas **Synopsys** NICTA and UNSW Computer Science Department, University of Oxford Microsoft Research Intel Northeastern University Microsoft Research Intel Corporation Galois, Inc. Yale University Linköping University **Synopsys** CISCO University of Lugano The Academic College of Tel Aviv Yaffo FormalSim Queen Mary University of London Vienna University of Technology Brno University of Technology Virginia Tech Technion Technische Universiät Wien

### Additional Reviewers

Alberti, Francesco Alpernas, Kalev Alt, Leonardo Aminof, Benjamin Andronick, June Asarin, Eugene Asathulla, Mudabir

Bannister, Callum Bjesse, Per Bortin, Maksym Bozga, Marius Brain, Martin Braud-Santoni, Nicolas

Calderon Trilla, Jose Manuel Cerny, Eduard Ceska, Milan Chakroborty, Souy Chen, Ben Chou, Cuong

Dang, Thao David, Cristina

Ebrahimi, Masoud Enea, Constantin

Fedyukovich, Grigory

Gopalakrishnan, Sivaram Graf, Susanne Guo, Shengjian

Hoenicke, Jochen Holik, Lukas Hyvärinen, Antti

Iabrudi, Andréa Ivrii, Alexander

Katelaan, Jens Khalimov, Ayrat Kini, Keshav Koenighofer, Bettina Kumar, Ramana

Leslie-Hurd, Joe

Mador-Haim, Sela Maranget, Luc Marescotti, Matteo Meshman, Yuri Moondanos, John Mukherjee, Rajdeep Murray, Toby

Nadel, Alexander Narayana, Srinivas Ngo, Van Chan Nonoshita, Hiroshi Norrish, Michael

Padon, Oded Palena, Marco Pani, Thomas Parizek, Pavel Parthasarathy, Ganapathy Partush, Nimrod Pasini, Paolo Peleg, Hila Petri, Gustavo Plassan, Guillaume Ponce-De-Leon, Hernan

Radicek, Ivan Rasin, Dan Reynolds, Andrew Roeck, Franz Roy, Tonmoy

Saarikivi, Olli Sangnier, Arnaud Santolucito, Mark Schrammel, Peter Seidl, Martina Selfridge, Ben Sinn, Moritz Sousa, Marcelo Sproston, Jeremy Subramanyan, Pramod Sung, Chungha

Vendraminetto, Danilo Vizel, Yakir

Westbrook, Edwin Winwood, Simon Wolfovitz, Guy Wu, Meng

Zeljić, Aleksandar Zhang, Naling Zhou, Min

# Table of Contents

| Formal Verification for Computer Security: Lessons Learned and Future Directions                                                                                                | 1   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Understanding Evolution through Algorithms                                                                                                                                      | 2   |

| Network Verification - When Clarke Meets Cerf                                                                                                                                   | 3   |

| Machine Learning and Systems for the Next Frontier in Formal Verification                                                                                                       | 4   |

| Verifying Hyperproperties of Hardware Systems                                                                                                                                   | 5   |

| A Paradigm Shift in Verification Methodology<br>Pranav Ashar                                                                                                                    | 6   |

| Program Synthesis for Networks                                                                                                                                                  | 7   |

| The FMCAD 2016 Graduate Student Forum                                                                                                                                           | 8   |

| Soundness of the Quasi-Synchronous Abstraction<br>Guillaume Baudart, Timothy Bourke and Marc Pouzet                                                                             | 9   |

| Synthesizing Adaptive Test Strategies from Temporal Logic Specifications                                                                                                        | 17  |

| Reducing Interpolant Circuit Size by Ad Hoc Logic Synthesis and SAT-Based Weakening<br>Gianpiero Cabodi, Paolo E. Camurati, Marco Palena, Paolo Pasini and Danilo Vendraminetto | 25  |

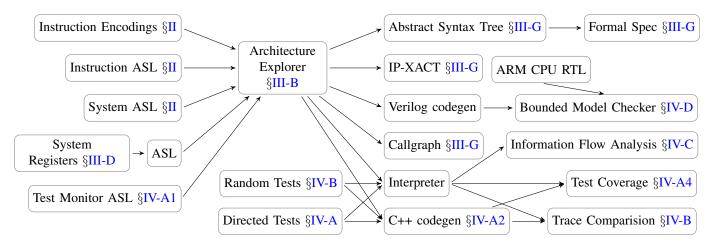

| Extracting Behaviour from an Executable Instruction Set Model<br>Brian Campbell and Ian Stark                                                                                   | 33  |

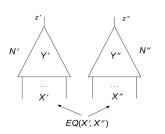

| Categorical Semantics of Digital Circuits<br>Dan Ghica and Achim Jung                                                                                                           | 41  |

| Equivalence Checking By Logic Relaxation                                                                                                                                        | 49  |

| Minimal unsatisfiable core extraction for SMT<br>Ofer Guthmann, Ofer Strichman and Anna Trostanetski                                                                            | 57  |

| Efficient Uninterpreted Function Abstraction and Refinement for Word-level Model Checking                                                                                       | 65  |

| Optimizing Horn Solvers for Network Repair                                                                                                                                      | 73  |

| On ∃∀∃! Solving: A Case Study on Automated Synthesis of Magic Card Tricks                                                                                                       | 81  |

| Property-Directed k-Induction<br>Dejan Jovanović and Bruno Dutertre                                                                                                             | 85  |

| Lazy Proofs for DPLL(T)-Based SMT Solvers                                                                                                                                       | 93  |

| Verifiable Hierarchical Protocols with Network Invariants on Parametric Systems                                                                                                 | 101 |

| Modular Specification and Verification of a Cache-Coherent Interface                                                          |

|-------------------------------------------------------------------------------------------------------------------------------|

| Proof Certificates for SMT-based Model Checkers for Infinite-state Systems                                                    |

| Routing under Constraints                                                                                                     |

| A Consistency Checker for Memory Subsystem Traces                                                                             |

| Hybrid Partial Order Reduction with Under-Approximate Dynamic Points-To and Determinacy Information                           |

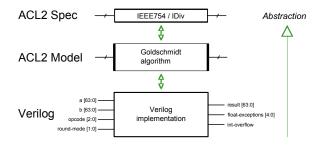

| Formal Verification of Division and Square Root Implementations, an Oracle Report                                             |

| Integrating Proxy Theories and Numeric Model Lifting for Floating-Point Arithmetic                                            |

| Trustworthy Specifications of ARM v8-A and v8-M System Level Architecture                                                     |

| Equivalence Checking Using Gröbner Bases       169         Amr Sayed-Ahmed, Daniel Grosse, Mathias Soeken and Rolf Drechsler  |

| Accurate ICP-based Floating-Point Reasoning                                                                                   |

| SWAPPER: A Framework for Automatic Generation of Formula Simplifiers based on Conditional Rewrite Rules                       |

| Lazy Sequentialization for TSO and PSO via Shared Memory Abstractions                                                         |

| Combining Requirement Mining, Software Model Checking, and Simulation-Based Verification for Industrial<br>Automotive Systems |

# Formal Verification for Computer Security: Lessons Learned and Future Directions

1

Dawn Song UC Berkeley

#### ABSTRACT OF INVITED TALK

Formal verification techniques have been fruitful for a broad spectrum of different security applications and domains. However, many important questions and considerations influence the success of applying formal verification techniques to security applications and domains. In this talk, I will share lessons learned from experience of over a decade in applying formal verification techniques to security. I will also discuss new exciting application domains such as blockchain and smart contracts for formal verification. I will pose important, open challenges and discuss future directions for verifying next-generation systems such as learning systems.

# Understanding Evolution through Algorithms

Christos Papadimitriou UC Berkeley

#### ABSTRACT OF INVITED TALK

Why is evolution so successful? What is the role of sex (recombination)? Why is there so much diversity in populations? How do novel traits arise? Are mutations random? And is evolution optimizing something? This talk will review recent work by the speaker and collaborators aiming at understanding the many persistent mysteries of evolution through computational ideas.

## Network Verification - When Clarke Meets Cerf

George Varghese UCLA

#### ABSTRACT OF INVITED TALK

Surveys reveal that network outages are prevalent, and that many outages take hours to resolve, resulting in significant lost revenue. Many bugs are caused by errors in configuration files which are programmed using arcane, low-level languages, akin to machine code. Taking our cue from program and hardware verification, we suggest fresh approaches. I will first describe a geometric model of network forwarding called Header Space. While header space analysis is similar to finite state machine verification, we exploit domain-specific structure to scale better than off-the shelf model checkers. Next, I show how to exploit physical symmetry to scale network verification for large data centers. While Emerson and Sistla showed how to exploit symmetry for model checking in 1996, they exploited symmetry on the logical Kripke structure. While header space models allow us to verify the forwarding tables in routers, there are also routing protocols such as BGP that build the forwarding tables. We show to go from header space verification to what we call control space verification to build a suite of tools for networks inspired by the Electronic Design Automation Industry. (With collaborators at CMU, Edinburgh, MSR, Stanford, and UCLA.)

# Machine Learning and Systems for the Next Frontier in Formal Verification

Manish Pandey Synopsys

ABSTRACT OF TUTORIAL TALK

This tutorial covers basics of machine learning, systems and infrastructure considerations for performing machine learning at scale, and applications of machine learning to improve formal verification performance and usability. It starts with blackbox classifier training with gradient descent, and proceeds on to deep network training and simple convolutional neural networks. Next, it discusses how machine learning can be performed at scale, overcoming the performance and throughput limitations of traditional compute and storage systems. Finally, the tutorial describes several ways in which machine learning can be applied for improving formal tools performance and enhancing debug capabilities.

# Verifying Hyperproperties of Hardware Systems

Bernd Finkbeiner Saarland University Markus Rabe UC Berkeley

#### ABSTRACT OF TUTORIAL TALK

This tutorial presents hardware verification techniques for hyperproperties. The most prominent application of hyperproperties is information flow security: information flow policies characterize the secrecy and integrity of a system by comparing two or more execution traces, for example by comparing the observations made by an external observer on execution traces that result from different values of a secret variable. Such a comparison cannot be represented as a set of traces and thus falls outside the standard notion of trace properties. A comparison between execution traces can, however, be represented as a set of sets of traces, which is called a hyperproperty. Hyperproperties occur naturally in many applications beyond their origins in security: examples include the symmetric access to critical resources in distributed protocols and Hamming distances between code words in coding theory.

The hardware verification approach of the tutorial is based on recently developed temporal logics for hyperproperties. Unlike classic temporal logics like LTL or CTL, *which refer to one computation path at a time, temporal logics for hyperproperties like HyperLTL and HyperCTL* can express properties that relate multiple traces by explicitly quantifying over multiple computation paths simultaneously. We will relate the logics to the linear-branching spectrum of process equivalences, and show that even though the satisfiability problem of the logics is undecidable in general, the model checking problem can be solved efficiently. We will show how the logics can be used to verify real hardware designs, including an I2C bus master, the symmetric access to a shared resource in a mutual exclusion protocol, and the functional correctness of encoders and decoders for error resistant codes.

### A Paradigm Shift in Verification Methodology

Pranav Ashar Real Intent

#### ABSTRACT OF TUTORIAL TALK

Todays SoCs are driving unprecedented verification complexity. The combination of billions of gates, system-level functionality on a chip, complex design methodologies like asynchronous clock domains and an explosion of untimed paths on a chip, interacting dynamic power domains, aggressive reset schemes etcetera could have been the perfect storm to staunch productivity. Instead it has turned out to be the mother of all necessities that has driven significant innovation in verification and brought about a paradigm shift.

Static sign-off has proven to be a pillar in this new paradigm. This talk will discuss the template for what has made static techniques successful in verifying modern SoCs. The recent successes are, in no small part, due to the FMCAD community that has pursued formal methods doggedly for decades despite glacial practical adoption. Complementing the efforts of the research community has been the equally determined pursuit in the EDA community to bring structure and automation into the verification process. Through this partnership, we have been able to bring about an analysis framework within which a combination of semantic analysis and formal methods enables a systematic verification process that leads to sign-off level confidence for important failure modes. It will be gratifying for the FMCAD audience to realize that SAT, model checking, functional abstraction, QBF etcetera have become essential in being able to tape out some of the most complex chips in the world on time and within budget. The adoption of IC3/PDR into the verification process was almost immediate.

The recent successes represent a strong debut for static methods. What is the vision to extend the promise into bigger slices of the verification pie? System-level verification continues to be an art-form with very little of the automation, process and problem-framing that have proven successful in other domains. May be the FMCAD community should adopt that as its next major challenge.

### Program Synthesis for Networks

Pavol Černý University of Colorado Boulder

#### ABSTRACT OF TUTORIAL TALK

Software is eating the world. But how will we write all the programs to control everything from sensors to data centers? Program synthesis provides an answer. It increases the productivity of programmers by enabling them to capture their insights in a variety of forms, not just in standard code. In this tutorial, we focus on some challenges in programming networks, and we show how program synthesis algorithms can help.

Developing network programs is difficult, as networks are large distributed systems. In particular, implementing programs that update the configuration of a network in response to events is an intricate problem. First, even if initial and final configurations are correct, subtle bugs in update programs can lead to incorrect transient behaviors, including forwarding loops, black holes, and access control violations. Second, if the update program reacts to events occurring near simultaneously in different parts of the network, naive implementations can lead to causality violations and conflicts. We present scalable program synthesis algorithms that produce network programs that are both correct by construction and efficient.

## The FMCAD 2016 Graduate Student Forum

Hossein Hojjat Computer Science Department Rochester Institute of Technology

*Abstract*—The FMCAD Student Forum provides a platform for graduate students at any career stage to introduce their research to the wider Formal Methods community, and solicit feedback. In 2016, the event took place in Mountain View, California, as integral part of the FMCAD conference. Ten students were invited to give a short talk and present a poster illustrating their work. The presentations covered a broad range of topics in the field of verification and synthesis, including automated reasoning, model checking of hardware, software, as well as hybrid systems, verification and synthesis of networks, and application of artificial intelligence techniques to circuit design.

Since 2013, the FMCAD conference features a Student Forum, providing a platform for graduate students at any career stage to introduce their research to the wider Formal Methods community. The FMCAD 2016 Graduate Student Forum follows the tradition of its predecessors, which took place in Austin, Texas, USA in 2015 [1], in Lausanne, Switzerland in 2014 [2] and in Portland, Oregon, USA in 2013 [3].

Graduate students were invited to submit short reports describing their ongoing research in the scope of the FMCAD conference. The submissions to the forum presented novel technical contributions and outlining future research planned by the authors. The presentations covered a broad range of topics in the field of verification and synthesis, including automated reasoning, model checking of hardware, software, as well as hybrid systems, verification and synthesis of networks, and application of artificial intelligence techniques to circuit design. Based on the reviews provided by members of the organizing committee as well as a number of external reviewers, 10 submissions were accepted. The reviews focused on the novelty of the work, the technical maturity of the submission, and the quality and soundness of the presentation. The following contributions have been accepted:

- Elaheh Ghassabani, Michael W. Whalen, Andrew Gacek, Rockwell Collins: "Inductive Validity Cores for Formal Verification"

- Yu-Yun Dai, Robert Brayton: "Circuit Recognition with Convolutional Neural Networks"

- Bo-Yuan Hunag, Pramod Subramanyan, Sharad Malik, Sayak Ray, Hareesh Khattri, Jason Fung, Abhranil Maiti: "Instruction-Level Abstraction Based SoC Firmware Verification"

- William Hallahan, Ruzica Piskac, Ennan Zhai, Avi Silberschatz: "Automated Firewall Repair with Example Synthesis"

- Hongce Zhang, Sharad Malik: "Equivalence Checking Using the Intermediate Instruction-Level Abstraction"

- Baoluo Meng: "Solving Relational Constraints with Ex-

tensions to a Theory of Finite Set in SMT"

- Mark Santolucito, Ruzica Piskac: "Version Space Learning for Verification on Temporal Differentials"

- Jaideep Ramachandran: "Precise Arithmetic Reasoning using Approximate Solvers"

- Rohit Dureja, Kristin Rozier: "Comparative Safety Analysis of Wireless Communication Networks in Avionics"

- Andres Noetzli: "Proofs for Preprocessing in SMT Solvers"

The 2016 student forum is the second in the series to feature a Best Contribution Award (based on the quality of the submission, the poster, and the presentation), announced during the conference and publicized on the FMCAD website.<sup>1</sup>

For the first time in the student forum series, we used a voting system to choose the best contribution. We allowed any participant (other than the authors and their supervisors) to vote for a single contribution. We created an electronic voting system and provided a link to the system in the registration packages of participants. Such a system offered several advantages. First of all, it inspired the poster presenters to do their best possible presentations for any participant, not only the referees who have a voice in determining the best contributions. Second, to increase the number of votes, the students were motivated to talk to more people and to try to attract their attentions to their posters. The overall experience was overwhelming in a more interactive poster session with more attendants.

The Student Forum would not have been possible without the excellent contributions of the student authors. The generous support of the National Science Foundation enabled us to subsidize the travel cost of the participating students. The help and advice of Georg Weissenbacher, who organized the previous student forums, as well as Sean Safarpour (Synopsys), who took care of local arrangements, was crucial to the success of the event. We are also indebted to Ruzica Piskac for her help with the reviews.

#### REFERENCES

- G. Weissenbacher, "The FMCAD 2015 graduate student forum," in Formal Methods in Computer-Aided Design (FMCAD). IEEE, 2015, p. 8.

- [2] R. Piskac, "The FMCAD 2014 graduate student forum," in Formal Methods in Computer-Aided Design (FMCAD). IEEE, 2014, p. 13.

- [3] T. Wahl, "The FMCAD graduate student forum," in Formal Methods in Computer-Aided Design (FMCAD). IEEE, 2013, pp. 16-17.

<sup>1</sup>http://www.cs.utexas.edu/users/hunt/FMCAD/FMCAD16/

## Soundness of the Quasi-Synchronous Abstraction

Guillaume Baudart<sup>\*‡</sup>

Timothy Bourke<sup>‡\*</sup>

Marc Pouzet<sup>\*†‡</sup>

\* École normale supérieure, PSL Research University

† Sorbonne Universités, UPMC Univ. Paris 06

‡ Inria Paris

Abstract—Many critical real-time embedded systems are implemented as a set of processes that execute periodically with bounded jitter and communicate with bounded transmission delay. The *quasi-synchronous abstraction* was introduced by P. Caspi for model-checking the safety properties of applications running on such systems. The simplicity of the abstraction is appealing: the only events are process activations; logical steps account for transmission delays; and no process may be activated more than twice between two successive activations of any other.

We formalize the relation between the real-time model and the quasi-synchronous abstraction by introducing the notion of a unitary discretization. Even though the abstraction has been applied several times in the literature, we show, surprisingly, that it is not sound for general systems of more than two processes. Our central result is to propose necessary and sufficient conditions on both communication topologies and timing parameters to recover soundness.

#### I. INTRODUCTION

The Synchronous Real-Time Model [2], [10] characterizes many distributed embedded systems: it applies whenever bounds exist on successive process executions and transmission delays. In particular, whenever computing units that execute periodically with jitter are connected together by network links. It is commonly employed in critical aerospace, power, and rail systems.

The quasi-synchronous approach [6], [8] formalizes a set of techniques for building distributed control systems that were observed by P. Caspi while consulting at Airbus on the distributed deployment of Lustre/SCADE<sup>1</sup> [17] designs. One of the key ideas is to model the computing units, network links, and shared memories themselves as a synchronous program [6, §3]. Such models can be verified using model-checking tools for discrete programs. This approach has, for instance, been applied to a Proximity Flight Safety (PFS) case-study from EADS Space Transportation [19] and to the analysis of systems specified in the Architecture Analysis and Design Language (AADL) [5], [20], [28].

An alternative way of developing real-time applications is to synchronize process executions. The Time-Triggered Architecture (TTA) [21], [22] thoroughly develops this approach and there are several clock synchronization protocols suitable for embedded systems. Once a clock

$^{\rm 1} \rm http://www.ansys.com/Products/Embedded-Software/ANSYS-SCADE-Suite$

synchronization scheme is adopted and assumed or verified correct, modeling and reasoning about applications is greatly simplified because non-determinism, in the form of possible interleavings, is either eliminated or reduced. The quasi-synchronous approach is nevertheless appropriate in certain applications either due to their simplicity, for example, microprocessors communicating directly over serial links, or the need for complete independence between subsystems, for example, as in redundant subnetworks connected only at voting units.

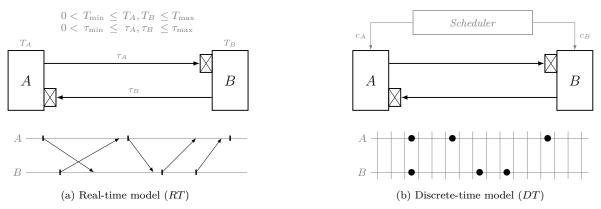

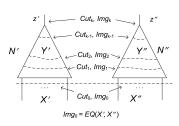

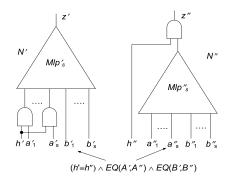

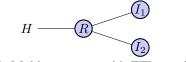

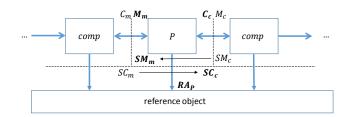

Figure 1 gives an overview of the quasi-synchronous approach. On the left is a real-time model comprising two processes, A and B, communicating through network links. Processes and links are annotated with timing bounds on executions ( $T_{\min}$  and  $T_{\max}$ ) and transmission delays ( $\tau_{\min}$  and  $\tau_{\max}$ ). Underneath is an example trace showing process activations and corresponding message transmissions. On the right is a discrete-time abstraction in which timing parameters are replaced by a discrete program called *Scheduler* that overapproximates their effect by controlling process activations, and, importantly, message transmissions are modeled by a single logical step. Underneath is a trace of the discrete-time model.

The ultimate aim is to verify properties of the real-time model in the simpler discrete-time model. The essential property is that every sequence of states that occurs in the real-time model can also occur in the discrete-time model.<sup>2</sup> Such an association guarantees soundness: all safety properties provable in the discrete-time model also hold of the real-time model. Since changes in state are directly related to received messages, we focus on traces without modeling process and network states explicitly. This means that a discrete model is a valid abstraction if every real-time trace has a discrete-time counterpart.

*Contributions:* We formalize the relation between realtime and discrete-time traces in the quasi-synchronous approach by introducing a *unitary discretization* based on the respective causality relations of the two models. With this tool we show that abstracting transmission delays as unit delays is not sound in general. We state and prove necessary and sufficient conditions on communication topologies and timing characteristics to recover soundness. We provide practical criteria for using the

$<sup>^{2}</sup>$ Assuming the state of the processes does not reference real time.

Fig. 1: Soundness: A property  $\varphi$  that can be verified in the discrete-time model will also holds for the real-time model,  $RT \models \varphi \iff DT \models \varphi$ .

quasi-synchronous abstraction to formally verify real-time systems in discrete-time model-checking tools [16], [18].

#### A. The Real-time Model

We consider the classic synchronous real-time model [2], [10], noting that 'synchronous' does not mean 'lock step'.

**Definition 1** (Synchronous Real-Time Model). A synchronous real-time model is a finite set of processes  $\mathcal{P}$ , where for every process, the delay T between two successive activations is bounded:

$$0 \le T_{\min} \le T \le T_{\max}.$$

(RP)

Values are transmitted between processes with a delay  $\tau \in \mathbb{R}$ , bounded by  $\tau_{\min}$  and  $\tau_{\max}$ :

$$0 \le \tau_{\min} \le \tau \le \tau_{\max}.$$

(RT)

Each message is buffered at receivers until a newer value is received. Execution time ( $\tau_{\text{exec}}$ ) can be modeled either as a part of the communication delay ( $\tau = \tau_{\text{exec}} + \tau_{\text{trans}}$ ), or as part of the activation period ( $\tau_{\text{exec}} < T_{\min}$ ) with the convention that application components communicate through logical delays: values computed in one reaction are sent at the beginning of the next one.

For readability, we assume global bounds on successive process activations, but our results are readily generalized to multirate systems.

#### B. The Discrete-time Model

The simplest discrete abstraction is the *asynchronous model* where time is ignored altogether and process activations may be interleaved arbitrarily. This is sound but far from complete: many properties that hold in the real-time model cannot be shown in the discrete one. Furthermore, the many possible interleavings complicate reasoning about or model-checking the discrete-time model.

A finer abstraction was proposed by Caspi for processes that execute 'almost periodically', that is,  $T_{\min} \approx T_{\max}$ . He realized that the interleavings of systems satisfying RP can be constrained  $[7, \S 3.2]$ :

It is not the case that a component process executes more than twice between two successive executions of another process.

Furthermore, he observed that when transmission delays are 'significantly shorter than the periods of [process activations]' they can be modeled by unit delays in the discrete-time model, but that 'if longer transmission delays are needed, modeling should be more complex' [6, §3.2.1]. A unit delay models the fact that a message sent at one logical instant is received at the next one.

More complex modeling refers to the standard approach of placing buffer processes between communicating processes. Such buffers provide receive and send events and maintain internal state to track messages in transmission. The quasi-synchronous abstraction eschews explicit link models thereby simplifying scheduling logic and halving the number of variables needed to model communication.

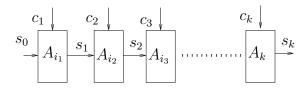

These observations allow abstraction from the timing details of the real-time model in definition 1 to give a nondeterministic and discrete-time model of systems termed *quasi-synchronous*. In the discrete-time model, boolean variables called *clocks* are set to *true* to activate processes.

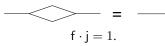

**Definition 2** (Quasi-Synchronous Model). A quasisynchronous model comprises a scheduler and finite set of processes  $\mathcal{P}$ . The scheduler is connected to each process by a discrete clock signal. It activates the processes nondeterministically but ensures that no pair of clock signals  $(c_A, c_B)$ , for a pair of processes  $A, B \in \mathcal{P}$ , ever contains the subsequence

$$\begin{bmatrix} t \\ - \end{bmatrix} \cdot \begin{bmatrix} f \\ f \end{bmatrix}^* \cdot \begin{bmatrix} t \\ f \end{bmatrix} \cdot \begin{bmatrix} f \\ f \end{bmatrix}^* \cdot \begin{bmatrix} t \\ - \end{bmatrix},$$

where t indicates an activation, f means no activation, and \_ means either of the two. Processes communicate through unit delays activated at every scheduler tick. This restriction on subsequences of pairs of clock signals [6, §3.2.2] expresses formally the constraint quoted beforehand. The forbidden subsequence involves at least three activations of one process (A) between two successive activations of another (B). A finite state scheduler that produces valid sequences is readily constructed from the given regular expression (using, for instance, the **reglo** tool [29]). The processes and unit delays can be modeled directly in Lustre [17], for instance, and verified by modelchecking [5], [19], [20], [28].

The quasi-synchronous model aims to reduce the statespace of a model in two ways: 1) by limiting the interleavings of process activations and 2) by simplifying message transmission modeling. In this paper, we show how the constraints imposed by the latter choice limit the applicability of the abstraction.

#### C. Relating Real time and Discrete time

Given definitions 1 and 2, it is natural to query the exact relationship between them, namely: what are necessary and sufficient conditions on the architecture to ensure the soundness of the abstraction?

The first step is to formalize real-time traces and their causality (section II). The main contribution of this paper is then to characterize the link between this causality relation and the causalities expressible in the discrete model. Specifically, we define a 'unitary discretization' that relates real-time traces to discrete-time traces (section III). It is quite constraining due to the modeling of communications as unit delays, but it still allows for the treatment of practically-relevant systems of two processes [19], [20] and those with certain communication topologies. Based on these results, we define precisely when the quasisynchronous model can be applied to a real-time system (section IV). We relate our work to classic distributed systems models, to the expression of causality in distributed systems, and to existing work on the quasi-synchronous abstraction (section V).

#### II. TRACES AND CAUSALITY

We define a formal model for reasoning about real-time models and their discretization. It has two components: (real-time) traces and their induced causality relations. In the following, we fix an arbitrary real-time model with processes  $\mathcal{P}$  and parameters  $T_{\min}$ ,  $T_{\max}$ ,  $\tau_{\min}$ , and  $\tau_{\max}$ that satisfy definition 1. We formalize pairs of sending and receiving processes using a *communicates-with* relation, written  $\Rightarrow$ , between the processes of a real-time model. This relation is not necessarily symmetric,  $A \Rightarrow B$  need not imply  $B \Rightarrow A$ , but it must be reflexive  $(A \Rightarrow A)$ .

**Definition 3** (Trace). A (real-time) trace  $\mathcal{E}$  is a set of activation events  $\{A_i \mid A \in \mathcal{P} \land i \in \mathbb{N}\}$  and two functions:

- $t(A_i)$ , the date of event  $A_i$  with respect to an ideal reference clock, and

- $\tau(A_i, B)$ , the transmission delay of the message sent at  $A_i$  to a process B.

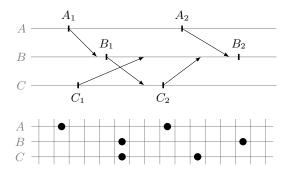

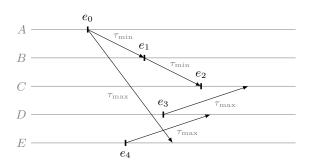

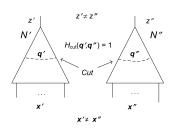

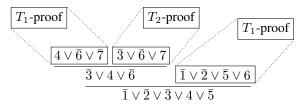

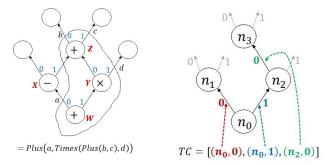

Fig. 2: A trace (above) and a possible unitary discretization.

Both  $t(A_i)$  and  $\tau(A_i, B)$  are non-negative reals satisfying the constraints of definition 1, namely if  $A \rightrightarrows B$ ,

$$0 \le T_{\min} \le t(A_{i+1}) - t(A_i) \le T_{\max}, and \\ 0 \le \tau_{\min} \le \tau(A_i, B) \le \tau_{\max}.$$

The causality relation between events within a given trace is essentially the *happened before* relation of Lamport [23]. Unlike Lamport, however, we do not explicitly model message reception. A message is received if the next execution of the receiver occurs after the corresponding transmission delay.

**Definition 4** (Happened Before). For a trace  $\mathcal{E}$ , let  $\rightarrow$  be the smallest relation on activation events that satisfies

(local) If

$$i < j$$

then  $A_i \to A_j$ , and

(recv) If  $A \rightrightarrows B$  and  $t(A_i) + \tau(A_i, B) \le t(B_j)$

then  $A_i \to B_j$ .

Activations at a single process are totally ordered (*local*); an activation at one process happens before an activation at another process when a message sent at the former is received before the latter (*recv*).

Compared to Lamport, we do not close the relation by transitivity. In this way,  $A_i \rightarrow B_j$  means that  $B_j$ occurs strictly after the reception of the message sent by process A at  $A_i$ . The same technique is used elsewhere [31, definition 1].

#### III. UNITARY DISCRETIZATION

We now address the central question of relating the realtime and discrete-time models. The problem is essentially one of correctly discretizing real-time traces.

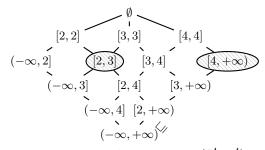

If process A sends messages to process B, the most general approach is to ensure that when an event  $A_i$  occurs before an event  $B_j$  in the discrete-time trace,  $A_i$  happens before  $B_j$   $(A_i \rightarrow B_j)$  in the corresponding real-time trace and vice versa. Figure 2 shows an example trace for a three-process system and a possible unitary discretization.

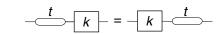

#### **Definition 5** (Unitary Discretization).

A function  $f : \mathcal{E} \to \mathbb{N}$  that assigns each event in a (realtime) trace to a logical instant of a corresponding discrete trace, is a unitary discretization if for all  $A_i, B_j \in \mathcal{E}$ ,

$$A_i \to B_j \iff (f(A_i) < f(B_j) \text{ and } A \rightrightarrows B)$$

. (UD)

Discretizing a real-time model satisfying definition 1 to a model of the form given in definition 2 amounts to finding a unitary discretization for *each* of its (real-time) traces. The forward half of the equivalence comes from the fact that the  $\rightarrow$  relation induces a partial order on events. Completing this relation to a total order gives a discretization that respects the causality of the real-time model [23].

A unitary discretization links the causality of events in the real-time model to the causality implicit in the discretetime model. The backward direction of the equivalence imposes that if an event y occurs after an event x in the discrete-time model, that is, f(x) < f(y), it is either because y is a later activation of the same process as x, or because y occurs strictly after the receipt of the message sent at x. It is the communication through unit delays on a common clock that tightly links the two causality relations.

In distributed systems terminology, condition UD is called *strong consistency* [30]. The problem of finding a unitary discretization is thus equivalent to the problem of finding a strongly consistent scalar clock. Raynal and Singhal report in their survey [30] that this is not possible in general, that is, there is no scalar clock function f that satisfies UD. This was already noted by Lamport in his original paper: 'We cannot expect the converse condition to hold as well [...]' [23, p.560].

The aim is to formulate sufficient conditions on the (static)  $\Rightarrow$  relation and on the timing characteristics of the real-time model to guarantee the existence of a unitary discretization. The following proposition will be useful.

**Proposition 1.** If f is a unitary discretization for a trace, for a pair of processes where  $A \rightrightarrows B$  we have that

$$A_i \to B_j \Longrightarrow f(A_i) < f(B_j), and$$

$A_i \to B_j \Longrightarrow f(A_i) \ge f(B_j).$

*Proof.* The first implication is a direct consequence of the definition of a unitary discretization. The second one follows by contraposition. If  $f(A_i) < f(B_j)$ , and since  $A \rightrightarrows B$ , we have  $A_i \rightarrow B_j$  by the definition of f.

An intermediate step to defining a static condition on communications is to characterize traces for which there is no unitary discretization. Our characterization will be based on a graph of the constraints of proposition 1.

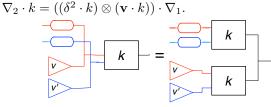

**Definition 6** (Trace Graph). Given a trace  $\mathcal{E}$ , its directed, weighted trace graph  $\mathcal{G}$  has as vertices  $\{A_i \mid A \in \mathcal{P} \land i \in \mathbb{N}\}$ and as edges the smallest relations that satisfy

1) If

$$A_i \to B_j$$

then  $A_i \xrightarrow{1} B_j$ , and

2) If  $A \rightrightarrows B$  and  $A_i \nrightarrow B_j$  then  $B_j \xrightarrow{0} A_i$ .

An example trace graph is shown in figure 3. Edges labeled with one  $(x \xrightarrow{1} y)$  represent the constraints f(x) < f(y). Each such edge indicates that the source activation must come before the destination activation in a unitary discretization, that is, the value of f, from source to destination, must increase by at least one. Edges labeled

Fig. 3: The trace (sub-)graph of the trace in figure 2. Black thick arrows denote  $x \xrightarrow{1} y/f(x) < f(y)$ . Thin gray arrows denote  $x \xrightarrow{0} y/f(x) \leq f(y)$ .

with zeros  $(x \xrightarrow{0} y)$  represent the constraints  $f(x) \leq f(y)$ . Each such edge indicates that the source activation cannot be placed before the destination activation in a unitary discretization, that is, the value of f, from source to destination, must be the same or larger. A path through several activations defines their relative ordering in all unitary discretizations.

The satisfaction of the required constraints, or the impossibility of satisfying them, can now be phrased in terms of cycles in the graph. A cycle comprising only  $\xrightarrow{0}$ 's is acceptable: its activations are all assigned the same discrete slot (for example,  $B_1$  and  $C_1$  in figure 3). Any cycle containing a  $\xrightarrow{1}$  represents a set of unsatisfiable constraints: one of the events must be placed in two different slots.

**Lemma 1** ( $\exists$ UD  $\iff \overline{\exists}PC$ ). For a trace  $\mathcal{E}$ , there is a unitary discretization ( $\exists$ UD) if and only if there is no cycle of positive weight in the corresponding trace graph  $\mathcal{G}$  ( $\overline{\exists}PC$ ).

*Proof.* Assume there is a cycle of positive weight. By the construction of  $\mathcal{G}$  there is an event x such that, for any unitary discretization function, f(x) < f(x), which is impossible.

Conversely, if there are no cycles of positive weight, we may define a function f that maps each event x to the weight of the longest path in  $\mathcal{G}$  that leads to x. By construction,  $A_i \to B_j \Longrightarrow f(A_i) < f(B_j)$ , which is the forward implication of UD (definition 5). The other direction of UD follows by contraposition. Assume  $A_i \not\to B_j$ . If  $A \rightrightarrows B$ , we have  $B_j \xrightarrow{0} A_i$  and thus, by the definition of f, that  $f(B_j) \leq f(A_i)$ . This gives  $\neg(f(A_i) < f(B_j))$  as required. The other case,  $A \not \equiv B$ , is trivial.  $\Box$

The unitary discretization described in the proof above is the most concise one and can be expressed as

$$f(x) = \max \left( \{ f(y) + 1 \mid y \xrightarrow{1} x \} \cup \{ f(z) \mid z \xrightarrow{0} x \} \cup \{ 0 \} \right).$$

Other discretizations are constructed by adding 'extra' instants between process activations as in figure 2.

#### A. Discretizing general systems

One might expect that real-time models are unitary discretizable if the transmission delays are 'significantly

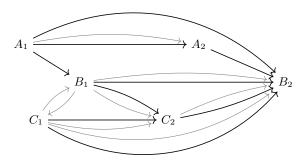

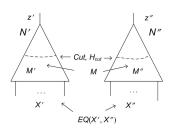

Fig. 4: A real-time trace that is not unitary discretizable  $(x \xrightarrow{1} y \xrightarrow{0} z \xrightarrow{0} x)$  and that may occur whenever  $\tau_{\max} > 0$ .

shorter' than the period of the process, that is  $\tau_{\rm max} \ll T_{\rm min}$ . Unfortunately this is not the case.

**Theorem 1** (No General Unitary Discretization). General real-time models with three processes or more communicating non-instantaneously are not unitary discretizable.

*Proof.* If  $\tau_{\text{max}} > 0$ , figure 4a shows a trace with a cycle of positive weight,  $x \xrightarrow{1} y \xrightarrow{0} z \xrightarrow{0} x$ , for which there is no unitary discretization (lemma 1).

Figure 4 shows the two possible discretizations of the counterexample. In figure 4b the message sent at z should have been received at  $y \ (z \to y)$ ; whereas in figure 4c the message sent at x should have been received at  $z \ (x \to z)$ . Neither correctly abstracts the real-time trace of figure 4a.

#### B. Recovering Soundness

The counterexample of figure 4 shows that when three processes communicate such that  $A \rightrightarrows B \rightleftharpoons C \rightleftharpoons A$ , there is at least one trace that has no unitary discretization. Problematic cycles in traces can be prevented either by constraining the timing parameters of the model or by restricting communication graphs: forbidding  $A \rightrightarrows B$ removes  $A_i \xrightarrow{1} B_j$  and  $B_j \xrightarrow{0} A_i$ , for all *i* and *j*, in associated trace graphs (if  $A \neq B$ ). We propose conditions that preclude cycles of positive weight in all possible traces and thus guarantee the existence of unitary discretizations.

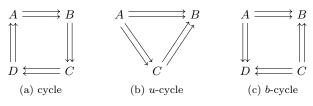

**Theorem 2.** Let  $L_c$  be the size of the longest elementary cycle in the communication graph. A real-time model satisfying definition 1 is unitary discretizable if and only if,

- 1) all u-cycles of the communication graph are cycles or balanced u-cycles, or  $\tau_{\text{max}} = 0$ , and

- 2) there is no balanced u-cycle in the communication graph or  $\tau_{\min} = \tau_{\max}$ , and

- 3) there is no cycle in the communication graph or

$$T_{\min} \ge L_c \tau_{\max}.$$

(CD)

A u-cycle is an elementary cycle in the undirected communication graph, that is, the graph obtained from the communication graph by forgetting the direction of

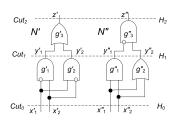

Fig. 5: Examples of communication topologies.

the edges. A balanced *u*-cycle has the same number of edges in both directions. Figure 5 shows three examples of *u*-cycles, the rightmost one is also a balanced *u*-cycle. In the following C, uC, and bC denote the sets of cycles, *u*-cycles, and balanced *u*-cycles, respectively.

In simpler terms, theorem 2 states that communication topologies containing *u*-cycles are only permissible if communication is perfectly instantaneous. Cycles can be allowed by imposing the additional constraint CD and balanced *u*-cycles can be allowed by imposing  $\tau_{\min} = \tau_{\max}$ . The following proposition is needed in the proof.

**Proposition 2.** If a trace graph has a cycle of positive weight, then it has a cycle of positive weight of the form:<sup>3</sup>

$$A^+ \xrightarrow{b_0} B^+ \xrightarrow{b_1} C^+ \xrightarrow{b_2} \dots \xrightarrow{b_n} A^+$$

where processes  $A, B, C, \ldots$  are pairwise distinct.

We write  $A^+$  to denote successive activations of process A.

*Proof.* From any cycle of positive weight one can build another cycle of positive weight with the correct form. The proof is given in the extended paper.  $\Box$

We now present a proof sketch for theorem 2, the complete proof can be found in the extended paper.

*Proof.* The proof is by contraposition in both directions. Using lemma 1 we have  $\exists UD \iff \exists PC$ . Therefore we prove the following statement, which is equivalent to theorem 2.

$$\exists c \in \mathcal{C} \text{ and } \overline{\mathrm{CD}}, \text{ or,}$$

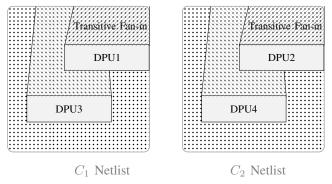

(C<sub>1</sub>)

$$\exists PC \iff \mid \exists c \in b\mathcal{C} \text{ and } \tau_{\min} < \tau_{\max}, \text{ or,}$$

(C<sub>2</sub>)

$$\exists c \in u\mathcal{C} \setminus (\mathcal{C} \cup b\mathcal{C}) \text{ and } \tau_{\max} > 0$$

(C<sub>3</sub>)

To prove that  $C_1$  or  $C_2$  or  $C_3 \implies \exists PC$  we show that in each of the three possible cases one can build a trace with a cycle of positive weight. Figure 6 shows such a counterexample for a *u*-cycle of 5 processes.

To prove that  $\exists PC \implies C_1$  or  $C_2$  or  $C_3$ , suppose that there exists a trace with a cycle of positive weight. By proposition 2, there also exists a trace with a cycle of positive weight of the form:

$$A^+ \xrightarrow{b_0} B^+ \xrightarrow{b_1} C^+ \xrightarrow{b_2} \dots \xrightarrow{b_n} A^+, \tag{1}$$

where processes A, B, C, ... are pairwise distinct. By proposition 2, for two processes A and B, a transition

${}^{3} \xrightarrow{b_{i}}$  is used as a generic notation for either  $\xrightarrow{1}$  or  $\xrightarrow{0}$ .

Fig. 6: Counterexample  $e_0 \xrightarrow{1} e_1 \xrightarrow{1} e_2 \xrightarrow{0} e_3 \xrightarrow{0} e_4 \xrightarrow{0} e_0$ , based on the *u*-cycle  $A \rightrightarrows B \rightrightarrows C \rightleftharpoons D \rightleftharpoons E \rightleftharpoons A$ .

$A_i \stackrel{0}{\to} B_j$  corresponds to a communication channel  $A \rightleftharpoons B$ with  $A \neq B$  and a transition  $A_i \stackrel{1}{\to} B_j$  corresponds to a communication channel in the opposite direction  $A \rightrightarrows B$ with the possibility that A = B for activations of the same process. Since the processes of (1) are pairwise distinct, the sequence of processes  $c = A, B, C, \ldots, A$  forms a *u*-cycle of the communication graph. There are three cases:

1)

$$c \in \mathcal{C}$$

imposes  $T_{\min} < L_c \tau_{\max}$  ( $\overline{\text{CD}}$ ), hence  $C_1$  holds.

- 2)  $c \in b\mathcal{C}$  imposes  $\tau_{\min} < \tau_{\max}$  and  $C_2$  holds.

- 3)  $c \in u\mathcal{C} \setminus (\mathcal{C} \cup b\mathcal{C})$  imposes  $\tau_{\max} > 0$  and  $C_3$  holds.

Theorem 1 is a particular case of theorem 2. Without assumptions on the communication graph there could be a u-cycle that is neither a cycle nor a balanced u-cycle.

**Corollary 1** (2-process Unitary Discretization). A realtime model satisfying definition 1 with two processes can be unitarily discretized if and only if

$$T_{\min} \ge 2\tau_{\max}.$$

(2D)

*Proof.* Direct consequence of theorem 2: for systems of two processes,  $L_c = 2$  and CD becomes  $T_{\min} \ge 2\tau_{\max}$ .

Two-process models were the focus of the original work on the quasi-synchronous approach [6] and they are relevant in practice [19], [20]. This result is coherent with Caspi's requirement that transmission delays be 'significantly shorter than the periods of [process activations]' [6, §3.2.1].

#### IV. THE QUASI-SYNCHRONOUS ABSTRACTION

We now apply the preceding definitions and results on unitary discretizations to precisely describe when the quasisynchronous model can be applied to a real-time system.

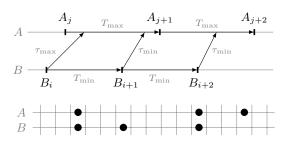

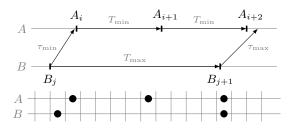

A discrete-time model is termed quasi-synchronous if 'it is not the case that a component process executes more than twice between two successive executions of another process' [7,  $\S3.2$ ]. Since any given process only detects the activations of another by receiving the corresponding messages, the quasi-synchronous condition corresponds to two constraints. For any process, 1) there are no more than two activations between two message receptions, and 2) there are no more than two message receptions between

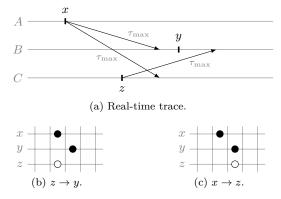

Fig. 7: A trace (above) and a possible discretization that violates definition 2.

two activations. This definition can be formalized using unitary discretizations.

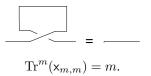

**Definition 7** (Quasi-Synchronous Model). A real-time model is quasi-synchronous if, for every trace t,

- 1) it has a unitary discretization f, and

- 2) for processes  $A \models B$ , there are no i and j such that

$$f(B_j) < f(A_i) < f(A_{i+2}) \le f(B_{j+1}) \text{ or,} f(A_j) \le f(B_i) < f(B_{i+2}) < f(A_{j+1}).$$

(QS)

This definition expresses the two central features of quasisynchrony: 1) communications as 'logical' unit delays, and 2) constraints on interleavings of process activations.

Condition QS is less constraining than definition 2 from section I-B. That definition, proposed by Caspi, has the advantage of forbidding a single symmetric subsequence, but the link with process interleavings is obscured. In fact, the proposition below shows that it is violated in any realtime system with unidirectional communications ( $A \rightleftharpoons B$ but  $A \not\rightrightarrows B$ ) that is not perfectly synchronous. So, while definition 7 does not directly translate definition 2, we argue that it more faithfully describes quasi-synchronous systems in terms of process interleavings.

**Proposition 3.** A pair of (real-time) processes A and B where  $A \coloneqq B$  but  $A \not \rightrightarrows B$  cannot be quasi-synchronous in the sense of definition 2 if  $T_{\min} + \tau_{\min} < T_{\max} + \tau_{\max}$ .

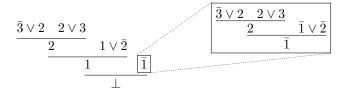

Proof. If  $T_{\min} + \tau_{\min} < T_{\max} + \tau_{\max}$ , figure 7 shows an execution trace where  $A_j \xrightarrow{0} B_i \xrightarrow{1} B_{i+1} \xrightarrow{1} A_{j+1} \xrightarrow{0} B_{i+2}$ . A discretization f with  $f(A_j) = f(B_i)$  and  $f(A_{j+1}) = f(B_{i+2})$  is a valid unitary discretization that violates the condition of definition 2.

While definition 7 conveys the essence of quasi-synchrony, its conditions are rather abstract. The following theorem incorporates the results of sections II and III to state concrete requirements on real-time parameters and communication topologies. The extended paper has a full proof.

**Theorem 3.** A real-time model satisfying definition 1 is quasi-synchronous (condition QS) if and only if,

- 1) the conditions of theorem 2 hold, and

- 2) the following condition holds,

$$2T_{\min} + \tau_{\min} \ge T_{\max} + \tau_{\max}.$$

(QT)

Fig. 8: Witness for  $QS \Longrightarrow QT$ .

*Proof.* The first condition ensures that the system is unitary discretizable. Now, if QS does not hold, there is a chain of events such that either

$$f(B_j) < f(A_i) < f(A_{i+2}) \le f(B_{j+1}) \text{ or,}$$

$$f(A_j) \le f(B_i) < f(B_{i+2}) < f(A_{j+1}).$$

This gives  $B_j \to A_i$ , and  $B_{j+1} \not\to A_{i+2}$  in the first case; and,  $B_i \not\to A_j$  and  $B_{i+2} \to A_{j+1}$  in the second; which implies  $2T_{\min} + \tau_{\min} < T_{\max} + \tau_{\max}$ , that is,  $\overline{\text{QT}}$ .

Conversely, if QT does not hold, then figure 8 shows a trace where  $B_j \xrightarrow{1} A_i \xrightarrow{1} A_{i+1} \xrightarrow{1} A_{i+2} \xrightarrow{0} B_{j+1}$ . Then, by definition 5, the discretization f such that

$$f(B_j) < f(A_i) < f(A_{i+2}) = f(B_{j+1}).$$

is a valid unitary discretization that violates QS.  $\hfill \Box$

Theorem 3 states precisely when the quasi-synchronous abstraction is sound. If a real-time system satisfies the given constraints on (logical) topology and timing, then the quasisynchronous abstraction can be used to formally verify its properties. To give a few concrete examples, providing condition QT holds, it applies to: 1) topologies without feedback, for example, three filter sequences connected to a triple voter; 2) trees of communicating pairs if  $T_{\min} \geq 2\tau_{\max}$ , for example, a 'daisy chain' or a star of intercommunicating neighbours; and 3) any feedback loop of n nodes if  $T_{\min} \ge n\tau_{\max}$ , for example, unidirectional ring networks or filters with 'non-overlapping' feedback loops. It does not apply if condition QT is violated, or in topologies with certain cycles, notably those with more than one path between two processes. The extended paper includes some examples of allowed and forbidden topologies.

#### V. Related Work

a) Distributed systems: The spectrum of formal models for distributed systems runs from completely synchronous (definition 1) to completely asynchronous [26]. The completely synchronous model makes the strongest timing assumptions—though they are not unreasonable for embedded systems—and it is possible to simulate roundbased applications and solve problems like consensus and leader election even in the presence of failures [2], [10].

The impossibility of consensus in the asynchronous model [14] and the desire to treat more general systems than the synchronous model motivates the study of *partially*  15

synchronous models [26, Part III]. There are models with bounds on transmissions and the relative speeds of processes, and these bounds are not necessarily known or may only hold eventually [12]. In the  $\theta$ -model [33] bounds are not given on transmissions but rather on the ratio of the longest and shortest end-to-end delays of messages simultaneously in transit. The *Finite Average Response* time model [13] only assumes a lower bound on activations and a finite average response time for transmissions. Timing assumptions may also be allowed to vary across different communication links [1]. The Asynchronous Bounded-Cycle model [31] avoids any reference to transmission delays or bounds on activations and instead constrains the causality chains induced by transmission.

We treat the standard synchronous distributed systems model and our treatment of causality and timing constraints has nothing to do with recovering possibility results or determining algorithmic complexity in a partially synchronous model. We study a different question: when is a very specific discrete abstraction sound for the synchronous real-time model? Our main problem comes from the unusual but potentially advantageous modeling of transmissions as unit delays. This gives rise to a unique form of causality—the unitary discretization—that is relevant to the model-checking problem we consider but not to the theory of distributed computing.

Unsurprisingly, our notion of causality follows Lamport's seminal work [23]. His causality relation was recently extended to a syncausality relation [3, Definition 2] by using upper bounds on transmission delays to complete causality chains. Our causality relation is similar but message reception is not modeled explicitly, the (recv)clause is based on actual transmission delays not an upper bound, and transitivity is not avoided. The syncausality relation is developed into 'centipede' and 'centibroom' abstractions to study coordination problems, whereas we develop the unitary discretization to verify the soundness of a discrete model. Our approach is closer to work on execution graphs [31]: we also use a non-transitive relation and count along causality chains. But our trace graphs incorporate two types of constraints  $(\xrightarrow{0} \text{ and } \xrightarrow{1})$  due to the different nature of the problem we study. Furthermore, the work on execution graphs focuses on asynchronous systems and does not propose constraining real-time parameters and communication topologies to eliminate cycles.

b) Logical clocks: As already mentioned in section III, the existence of a unitary discretization is equivalent to the problem of finding a strongly consistent scalar clock. As this is not possible in general [23], [30], research has sought more powerful mechanisms, like vector clocks [27] and matrix clocks [15], for capturing the causalities of events. These mechanisms do not resolve the problem posed in this paper, since the modeling of transmissions as unit delays and the activations of processes on boolean streams require the total ordering given by a global scalar clock: a synchronous modeling of an asynchronous system. c) Quasi-synchrony: Most existing work on the quasisynchronous abstraction either assumes instantaneous communication [5], [28]—which may be valid in a shared memory model but not a message-passing one—or takes the discrete model as given and applies it directly to model and analyze systems [19], [20], [32]. We seek to clarify the original definitions [6] and to precisely define the relation between the real-time and discrete-time models. This leads to the understanding of discretization in terms of causality and the restrictions on process intercommunications and timing which are the central contributions of this paper.

Our work is complementary to the development of abstract domains to statically analyze synchronous realtime systems [4], and to the verification of properties like maximal lost messages, message inversions, and message latency, in an interactive theorem prover [24], [25].

In *n*-synchrony, unlike in *quasi-synchrony*, the difference of cumulative process activation counts is bounded [9]. The relation between a similar model and real-time has recently been studied [11]. Both *n*-synchrony and quasi-synchrony can be related to 'clock bounds' and 'drift bounds' [32].

#### VI. CONCLUSION

The quasi-synchronous abstraction provides a way to model and reason about a class of distributed embedded systems whose processes communicate by sampling with bounded jitter. Given a real-time model satisfying certain constraints on timing parameters and communication topologies, properties obtained of the corresponding quasisynchronous model are also true of the original model. In other words, a precise class of practically-relevant distributed control systems can be verified without resorting to timed formalisms and tools, and by modeling message transmission as a unit delay, but not all of them.

#### Acknowledgments

We thank Cesare Tinelli for sharing his experiences on model-checking quasi-synchronous models and Thibault Rieutord and our anonymous reviewers for their suggestions and comments.

#### References

- M. K. Aguilera, C. Delporte-Gallet, H. Fauconnier, and S. Toueg. Communication-efficient leader election and consensus with limited link synchrony. In *PODC*, pages 328–337, 2004.

- [2] H. Attiya, C. Dwork, N. Lynch, and L. Stockmeyer. Bounds on the time to reach agreement in the presence of timing uncertainty. *JACM*, 41(1):122–152, 1994.

- [3] I. Ben-Zvi and Y. Moses. Beyond Lamport's happened-before: On time bounds and the ordering of events in distributed systems. In *DISC*, pages 421–436, 2010.

- [4] J. Bertrane. Static analysis of communicating imperfectly-clocked synchronous systems using continuous-time abstract domains. PhD thesis, École Polytechnique, 2008.

- [5] S. Bhattacharyya, S. Miller, J. Yang, S. Smolka, B. Meng, C. Sticksel, and C. Tinelli. Verification of quasi-synchronous systems with Uppaal. In *DASC*, pages 8A4–1–8A4–12, 2014.

- [6] P. Caspi. The quasi-synchronous approach to distributed control systems. Technical Report CMA/009931, Verimag, Crysis Project, 2000. "The Cooking Book".

- [7] P. Caspi. Embedded control: From asynchrony to synchrony and back. In *EMSOFT*, pages 80–96, 2001.

- [8] P. Caspi, C. Mazuet, and N. Reynaud Paligot. About the design of distributed control systems: The quasi-synchronous approach. In SAFECOMP, pages 215–226, 2001.

- [9] A. Cohen, M. Duranton, C. Eisenbeis, C. Pagetti, F. Plateau, and M. Pouzet. N-synchronous Kahn networks: a relaxed model of synchrony for real-time systems. In *POPL*, pages 180–193, 2006.

- [10] F. Cristian. Synchronous and asynchronous group communication (long version). CACM, 1996.

- [11] A. Desai, S. A. Seshia, S. Qadeer, D. Broman, and J. C. Eidson. Approximate synchrony: An abstraction for distributed almostsynchronous systems. In CAV, pages 429–448, 2015.

- [12] C. Dwork, N. Lynch, and L. Stockmeyer. Consensus in the presence of partial synchrony. JACM, 35(2):288–323, 1988.

- [13] C. Fetzer, U. Schmid, and M. Süßkraut. On the possibility of consensus in asynchronous systems with finite average response times. In *ICDCS*, pages 271–280, 2005.

- [14] M. J. Fischer, N. A. Lynch, and M. S. Paterson. Impossibility of distributed consensus with one faulty process. *JACM*, 32(2):374– 382, 1985.

- [15] M. J. Fischer and A. Michael. Sacrificing serializability to attain high availability of data in an unreliable network. In *PODS*, pages 70–75, 1982.

- [16] G. Hagen and C. Tinelli. Scaling up the formal verification of Lustre programs with SMT-based techniques. In A. Cimatti and R. B. Jones, editors, *FMCAD*, pages 15:1–15:9, 2008.

- [17] N. Halbwachs, P. Caspi, P. Raymond, and D. Pilaud. The synchronous dataflow programming language Lustre. *Proc. IEEE*, 79(9):1305–1320, 1991.

- [18] N. Halbwachs, F. Lagnier, and C. Ratel. Programming and verifying real-time systems by means of the synchronous dataflow language LUSTRE. *IEEE Trans. Software Engineering*, 18(9):785-793, 1992.

- [19] N. Halbwachs and L. Mandel. Simulation and verification of asynchronous systems by means of a synchronous model. In ACSD, pages 3–14, 2006.

- [20] E. Jahier, N. Halbwachs, and P. Raymond. Synchronous modeling and validation of schedulers dealing with shared resources. Technical Report 2008-10, Verimag, 2008.

- [21] H. Kopetz. Real-time systems: design principles for distributed embedded applications. Springer-Verlag, 2011.

- [22] H. Kopetz and G. Bauer. The time-triggered architecture. Proc. IEEE, 91(1):112–126, 2003.

- [23] L. Lamport. Time, clocks, and the ordering of events in a distributed system. CACM, 21(7):558–565, 1978.

- [24] R. Larrieu and N. Shankar. A framework for high-assurance quasi-synchronous systems. In MEMOCODE, pages 72–83, 2014.

- [25] W. Li, L. Gérard, and N. Shankar. Design and verification of multi-rate distributed systems. In *MEMOCODE*, pages 20–29, 2015.

- [26] N. A. Lynch. Distributed Algorithms. Morgan Kaufmann, 1996.

[27] F. Mattern. Virtual time and global states of distributed systems.

- Parallel and Distributed Algorithms, 1(23):215–226, 1989.

- [28] S. Miller, S. Bhattacharyya, C. Tinelli, S. Smolka, C. Sticksel, B. Meng, and J. Yang. Formal verification of quasi-synchronous systems. Technical report, DTIC Document, 2015.

- [29] P. Raymond. Recognizing regular expressions by means of dataflow networks. In *ICALP*, pages 336–347, 1996.

- [30] M. Raynal and M. Singhal. Logical time: Capturing causality in distributed systems. *IEEE Computer*, 29(2):49–56, 1996.

- [31] P. Robinson and U. Schmid. The asynchronous bounded-cycle model. TCS, 412(1):5580–5601, 2011.

- [32] G. Smeding and G. Goessler. A correlation preserving performance analysis for stream processing systems. In *MEMOCODE*, pages 11–20, July 2012.

- [33] J. Widder and U. Schmid. The theta-model: achieving synchrony without clocks. *Distributed Computing*, 22(1):29–47, 2009.

# Synthesizing Adaptive Test Strategies from Temporal Logic Specifications

Roderick Bloem\*, Robert Könighofer\*, Ingo Pill<sup>†</sup>, and Franz Röck\*

\*Institute of Applied Information Processing and Communications, Graz University of Technology, Austria <sup>†</sup>Institute of Software Technology, Graz University of Technology, Austria

Abstract-Constructing good test cases is difficult and timeconsuming, especially if the system under test is still under development and its exact behavior is not yet fixed. We propose a new approach to compute test cases for reactive systems from a given temporal logic specification. The tests are guaranteed to reveal certain simple bugs (like occasional bit-flips) in every realization of the specification and for every behavior of the uncontrollable part of the system's environment. We aim at unveiling faults for the lowest of four fault occurrence frequencies possible (ranging from a single occurrence to persistence). Based on well-established hypotheses from fault-based testing, we argue that such tests are also sensitive for more complex bugs. Since the specification may not define the system behavior completely, we use reactive synthesis algorithms (with partial information) to compute adaptive test strategies that react to behavior at runtime. We work out the underlying theory and present first experiments demonstrating that our approach can be applied to industrial specifications and that the resulting strategies are capable of detecting bugs that are hard to detect with random testing.

#### I. INTRODUCTION

Model checking [12], [42] cannot always be applied effectively to obtain confidence in the correctness of a system. Possible reasons include scalability issues, third-party IP components for which no code or detailed model is available, or a high effort for building system models that are sufficiently precise. Moreover, model checking cannot verify the final and "live" product but only an (abstracted) model.

Testing is a natural alternative to complement formal methods, and automatic test case generation helps keeping the effort manageable. Black-box techniques, where tests are derived from a specification rather than the implementation, are particularly attractive: First, tests can be computed before the implementation work starts, and can thus guide the development. Second, the same tests can be reused across different realizations of the same specification. Third, a specification is usually much simpler than its implementation, which gives a scalability advantage. At the same time, the specification focuses on the critical aspects that require thorough testing. Fault-based techniques [26], where test cases are computed to reveal certain fault classes, are particularly appealing — after all, the foremost goal in testing is to detect bugs.

Methods to derive tests from declarative requirements (see, e.g., [23]) are sparse. One issue in this setting is controllability: the requirements leave plenty of implementation freedom, so

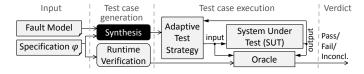

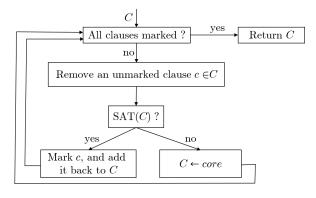

Fig. 1. Our testing setup. This paper focuses on test strategy synthesis.

they cannot be used to fully predict the system behavior for given inputs. Consequently, test cases have to be *adaptive*, i.e., able to react to observed behavior at runtime, rather than being fixed input sequences. This is particularly true for *reactive systems* that interact with their environment. Existing methods often work around this complication by requiring a deterministic system model as additional input [22]. Even a probabilistic model fixes the behavior in a way not necessarily required by the specification.